#### Soumak

How rich descriptions enable early detection of hookup issues

Peter Birch and Thomas Brown, Graphcore

GRAPHCORE

#### Overview

- Scale and complexity at Graphcore

- Constructing subsystems and chips

- Existing solutions

- Goals in developing a new solution

- Introduction to Soumak

- Shift-left of issue detection

# Scale and Complexity

- Reticle-scale die with 59.4 billion transistors

- 1,472 instances of the Tile processor

- Numerous SERDES interfaces for Ethernet & PCIe

- Subsystems are complex and deeply hierarchical

- Hundreds of components

- Thousands of connections

- Many distinct signal types

### Constructing Complex Subsystems

- Infeasible in SV/VHDL

- Connectivity is horrendous

- Thousands of connections

- Many similarly named and sized signals

- Verbose syntax

- Chances of an error are high

- Lint can only help so much

- Exhaustive simulation and formal proof infeasible at these scales

#### Abstractions

- Deeper hierarchy

- Related modules can be grouped together to contain wiring

- Can lead to repetitive hierarchical connections

- Use SV/VHDL interfaces

- Grouped signals reduce complexity, lower chance of an error

- Commercial tool support is highly variable

- Describe connectivity at a higher level

- Use another language to describe (and automate) connectivity

### **Existing Solutions**

- Accelera IP-XACT

- Syntax focused on machine readability, not hand editing

- EDA tooling required to generate RTL

- Tool APIs and reporting limit custom flows

- Alternative HDLs like Chisel (Scala) & Amaranth (Python)

- Partial adoption is difficult

- Shims around SV/VHDL can be painful

#### Requirements

- Concise syntax for describing connectivity

- Tight integration with existing SystemVerilog design

- Support for:

- Nested interfaces

- Constants, typedefs, and data structures

- Topologies such as rings, chains, and meshes

- Early-as-possible sanity checks

- Support for backends such as code generation

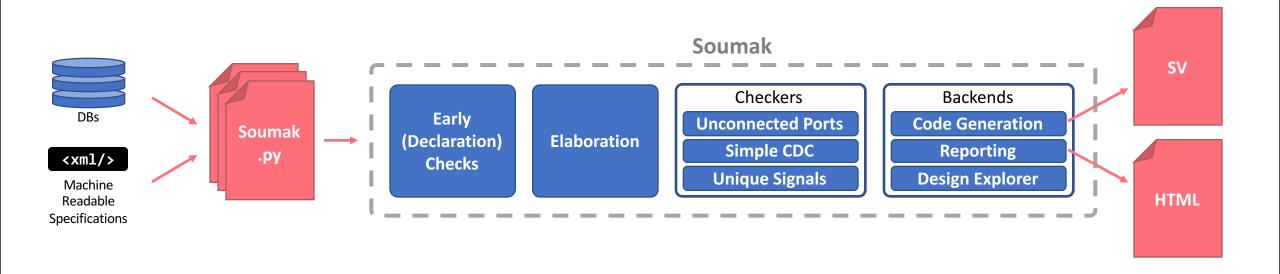

#### Workflow

# Defining a Leaf Node

```

import soumak

from soumak import In, Out

from soumak.signal import Clock, Reset

@soumak.block()

class Hexcpu:

clk : In(Clock)

rst : In(Reset)

fault : Out(width=1, desc="Internal error occurred")

```

```

hexcpu

clk

fault

rst

```

hexcpu.py

# Defining a Leaf Node

Decorators check hardware definition - on declaration

```

import soumak

from soumak import In, Out

from soumak.signal import Clock, Reset

@soumak.block()

class Hexcpu:

clk : In(Clock)

rst : In(Reset)

fault : Out(width=1, desc="Internal error occurred")

Built-in primitive

signal types

Decorator reads and

checks the type

annotations

```

hexcpu.py

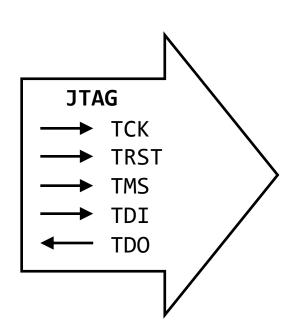

#### Interfaces

```

import soumak

from soumak import Request, Response

from soumak.signal import Clock, Reset

@soumak.interface()

class JTAG:

""" JTAG bus definition """

tck : Request(Clock)

trst : Request(Reset)

tms : Request(desc="Mode select")

tdi : Request(desc="Test data in")

tdo : Response(desc="Test data out")

```

jtag.py

#### Interfaces

import soumak from soumak import Request, Response from soumak.signal import Clock, Reset @soumak.interface() class JTAG: Comments are stored JTAG bus definition with each declaration : Request(Clock) trst : Request(Reset) Base signal types & : Request(desc="Mode select") : Request(desc="Test data in") other interfaces can : Response(desc="Test data out") be referenced

Signals can travel with or against the interface

jtag.py

### Types & Constants

```

import soumak

from soumak import Constant, Typedef

@soumak.package()

class HexPackage:

# === Constants ===

ADDR_W : Constant(desc="Width of address bus" ) = 32

DATA_W : Constant(desc="Width of the data bus" ) = 32

BYTE_W : Constant(desc="Data bus width in bytes") = (DATA_W / 8)

# === Types ===

data : Typedef(width=DATA_W, desc="Type for carrying data")

```

hex\_package.py

**Explicit values and**

arithmetic is fully

supported

Simple data types can

be declared

#### Enumerations

Implicit or explicit value assignments

Supports indexing, one-hot, and Gray coding

hex\_package.py

#### Structs & Unions

References can be made to enums, structs, and unions

```

@soumak.struct(package=HexPackage, width=32)

class DMAWriteRequest:

: Instance(DMATransfer,

desc="Type of transfer"

mode

address : Scalar(width=HexPackage.ADDR_W, desc="Where to write data"

: Scalar(width=16,

desc="How many bytes to write"

length

exclusive : Scalar(width=1,

desc="Lock memory during transfer")

@soumak.struct(package=HexPackage, width=32)

class DMAReadRequest:

: Instance(DMATransfer,

desc="Type of transfer"

mode

: Scalar(width=HexPackage.ADDR_W, desc="Where to read data from")

address

: Scalar(width=16,

desc="How many bytes to read" )

length

@soumak.union(package=HexPackage)

class DMARequest:

write : Instance(DMAWriteRequest)

read : Instance(DMAReadRequest)

```

hex\_package.py

# Interfacing with SystemVerilog

```

package hex_package;

localparam ADDR_W = 32; // Width of address bus

localparam DATA_W = 32; // Width of data bus

localparam BYTE_W = 4; // Data bus width in bytes

typedef logic [31:0] data_t; // Type for carrying data

typedef enum logic [2:0] {

IDLE = 3'b001 // Waiting for new DMA request

, BUSY = 3'b010 // Busy processing memory operation

, FAULT = 3'b100 // Error occurred while moving data

} dma_state_t;

```

hex\_core.py

```

from .hex_package import HexPackage

@soumak.block()

class HexDMA:

clk : In(Clock)

rst : In(Reset)

request : In(HexPackage.DMARequest)

state : Out(HexPackage.DMAState)

# ...other signals...

```

hex\_dma.py

```

• • •

from .hex_core import HexCore

from .hex_dma import HexDMA

from .jtag import JTAG

@soumak.block()

class HexSubsystem:

# === Ports ===

: In(Clock)

: In(Reset)

debug : In(JTAG)

# === Children ===

: Instance(HexCore)

: Instance(HexDMA)

# === Connectivity ===

def connect(self):

self.fanout(self.clk, self.all_children.clk)

self.fanout(self.rst, self.all children.rst)

self.link(self.debug, self.core.debug)

self.link(self.core.dma_req, self.dma.request)

self.link(self.dma.state, self.core.dma_state)

```

```

hex_subsystem

□ clk

□ rst

debug

hex_dma

hex_core

└└ clk

└ clk

dma_req 中

→ロ rst

·□ rst

dma_state 口←

中 request

•坤 debug

state

```

```

• • •

from .hex_core import HexCore

from .hex_dma import HexDMA

from .jtag import JTAG

@soumak.block()

class HexSubsystem:

# === Ports ===

: In(Clock)

: In(Reset)

debug : In(JTAG)

# === Children ===

: Instance(HexCore)

: Instance(HexDMA)

# === Connectivity ===

def connect(self):

self.fanout(self.clk, self.all_children.clk)

self.fanout(self.rst, self.all_children.rst)

self.link()self.debug, self.core.debug)

self.link(self.core.dma_req, self.dma.request)

self.link(self.dma.state, self.core.dma_state)

```

```

hex_subsystem

□ clk

□ rst

debug

hex_dma

hex_core

└└ clk

└ clk

dma_req 中

→ロ rst

·□ rst

dma_state 中₁

🗘 request

•坤 debug

state

```

```

• • •

from .hex_core import HexCore

from .hex_dma import HexDMA

from .jtag import JTAG

@soumak.block()

class HexSubsystem:

# === Ports ===

: In(Clock)

: In(Reset)

debug : In(JTAG)

# === Children ===

core : Instance(HexCore)

: Instance(HexDMA)

# === Connectivity ===

def connect(self):

self.fanout(self.clk, self.all_children.clk)

self.fanout(self.rst, self.all children.rst)

self.link(self.debug, self.core.debug)

self.link(self.core.dma_req, self.dma.request)

self.link(self.dma.state, self.core.dma_state)

```

all\_children is expanded during elaboration, allowing multiple connections to be formed with a single statement

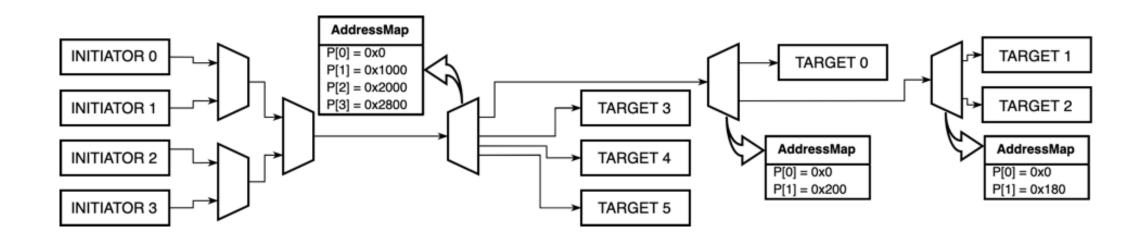

### Topologies

- Rings, chains, and meshes topologies can be constructed using special 'traits'

- Multiple complex connections can be formed with just a single statement

- Design tracks which connection patterns have been added

self.nodes.all.inbound expands in elaboration to create a list of all inbound access ports

#### Benefits

- Fewer connection statements

- Concise and easy to audit code

- Less chance of a mistake

- Strict type checks

- Impossible to connect incompatible signals without an explicit cast

- Fewer lines of code to audit

- Works for single wires and complex buses

#### Declaration Checks

#### Checks on Declarations

```

@soumak.enum(package=DesignPkg, width=1)

class MessageType:

""" Different types of messages sent over the bus """

NOP : Constant("Perform no operation")

WRITE : Constant("Perform a write operation")

READ : Constant("Perform a read operation")

```

```

/a/work/peterb/sili/workspace_one/colossus-silicon/lib/soumak/examples/packages/design.py:28 in <module>

25 | Token : Typedef( 4, "Access token" )

26 | 27 @soumak.enum(package=DesignPkg, width=1)

) 28 class MessageType:

29 | """ Different types of messages sent over the bus """

30 | NOP : Constant("Perform no operation")

31 | WRITE : Constant("Perform a write operation")

/a/work/peterb/sili/workspace_one/colossus-silicon/lib/soumak/soumak/_init__.py:319 in do_inner

/a/work/peterb/sili/workspace_one/colossus-silicon/lib/soumak/soumak/meta/enum.py:63 in _sk_construct

SoumakFieldError: Entry 'READ' of MessageType takes value 2 which exceeds the bit width of 1

```

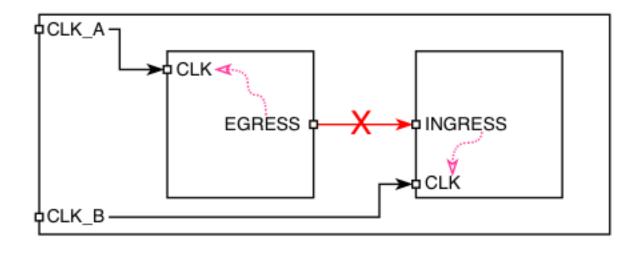

### Checks During Elaboration

# Checks on the Assembled Design

[12:12:01] ERROR checker.clocking: Connection in 'Top' made between 'Top.blk\_a.egress' and 'Top.blk\_b.ingress' spans between report.py:144

two different clock domains 'Top.blk\_a.clk' and 'Top.blk\_b.clk'

# Precise Sign-offs

```

@soumak.block()

class Top:

# ...

def signoff(self):

yield Signoff.okay("clocking",

extra=(self.blk_a.egress)

self.blk_b.ingress)

```

### Summary

- Assembling reticle sized ASICs is a difficult task

- Soumak abstracts the assembly of subsystems

- Shared constants and types softens boundary between tools

- Complex interface descriptions reduces wiring verbosity

- Python can be leveraged to automate connectivity

- Rich descriptions enable earlier checks

- Strict type checking helps to reduce mistakes

- Analysis flows can crawl through elaborated designs

- Checkers can flag gross issues early in the design process